锁存器Latch与触发器flipflop有什么区别

来源:电工天下时间:2020-02-24 08:52:15 作者:老电工手机版>>

锁存器Latch与触发器flipflop有什么区别

1、锁存器Latch 和 触发器flipflop

锁存器能根据输入端把结果自行保持;触发器是指由时钟边沿触发的存储器单元;

由敏感信号(电平,边沿)控制的锁存器就是触发器;

2、写电路时产生锁存器的原因

if语句中,没有写else,默认保持原值,产生锁存器,可能不是想要的结果;

case语句中,没有写完整default项,也容易产生锁存器;

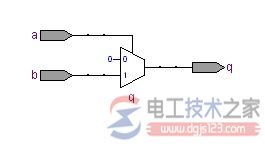

例子:

always@(a or b)

begin

if(a) q=b;

end

产生了锁存器,如下

没有锁存器的情况

always@(a or b)

begin

if(a) q=b;

else q=0;

end

3、避免使用D锁存器,尽量使用D触发器

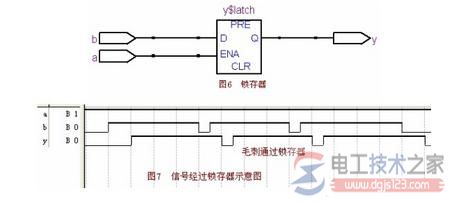

D锁存器

module test_latch(y, a, b);

output y; input a; input b; reg y;

always @(a or b) begin

if(a==1’b1)

y=b;

end endmodule

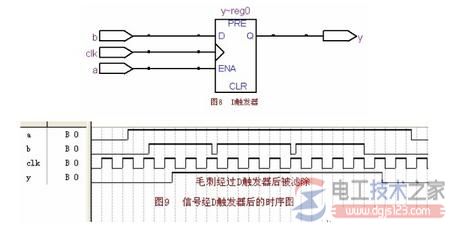

D触发器

module test_d(y,clk,a,b);

output y; input clk; input a; input b; reg y;

always @(posedge clk) begin

if(a==1'b1)

y=b;

end endmodule

从图8可知,例10对应的电路是D触发器。信号a被综合成D触发器的使能端,只有在时钟上沿到来且a为高时,b信号的值才能传递给a;只要在时钟上升沿期间信号b是稳定,即使在其他时候b还有毛刺,经过D触发器后数据是稳定的,毛刺被滤除。

相关文章断路器脱扣与跳闸有什么区别

有关断路器脱扣与跳闸的区别,断路器在合闸过程中,保护动作接通跳闸回路,断路器能可靠地断开为自由脱扣,跳闸则是线路故障,或电路过载,引起的断路器断开,称为跳闸。

时间:2022-08-31 11:37:47

家中漏电装置和空气开关的几点区别

在家中装修时必须装上空气开关,也有人会同时装上漏电保护,那么二者有什么联系,家中漏电装置和空气开关的区别有哪些,下面来看下。

时间:2021-12-03 05:25:04

3p空气开关接线图 3P与4P的区别

3p空气开关接线图,3P与4P的区别,注意输入输出不能接反,接反烧漏电保护器脱扣线圈,电源接漏电保护器的电源侧(上端),漏电保护器负荷侧接负载,3P与4P的区别在于3P无零线,4P有零线。

时间:2021-09-30 09:19:25

空开C型和D型有什么区别

有关空气开关的小知识,空开有C型和D型等不同类型,那么C型和D型有什么区别,在空开上的字母含义是什么,很多电工朋友不是很了解,下面就一起来看下。

时间:2021-09-11 19:28:21

万能断路器与真空断路器的区别是什么

有关万能断路器与真空断路器的区别,真空断路器和真空接触器有何区别,真空断路器触头有哪些种类,固封断路器与普通真空断路器的区别等。

时间:2021-09-07 16:04:12

一文看懂不同触点断路器的区别

有关断路器的基本知识,断路器上标注有1p、2p、3p、4p这样的字眼,究竟是什么意思,它是代表不同的触点,这里介绍下不同触点断路器的区别,供大家参考。

时间:2021-05-11 14:36:31

断路器1P、2P、3P、4P的功能区别

有关断路器的知识,不同的断路器有不同的触点开关,比如1P、2P、3P、4P,触点不同其应用场合就不同,这里说一说断路器1P、2P、3P、4P的功能区别,供大家参考。

时间:2021-05-11 14:33:13

断路器1P、2P、3P、4P有什么区别

有关断路器的知识,断路器1P、2P、3P、4P有什么区别,在家庭线路中如何选用不同类型的断路器,比如器1P、2P用在什么地方,3P、4P又该怎么选择,下面一起来了解下。

时间:2021-05-11 14:02:34

- 上一篇:断路器Icu与Ics是什么意思

- 下一篇:交流断路器在直流电路中的应用要点