555定时器集成芯片引脚图及引脚功能

来源:电工天下时间:2021-07-31 20:52:45 作者:老电工手机版>>

有关555定时器的小知识,介绍下555定时器集成芯片引脚图,以及555定时器集成芯片的八个引脚功能,比如1脚为外接电源负端VSS或接地,2脚低触发端TL,一起来了解下。

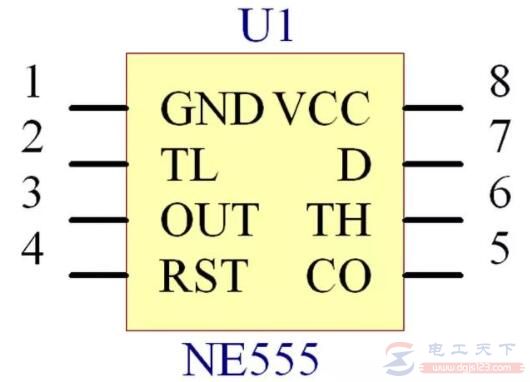

一、555定时器集成芯片引脚图

引脚图如下:

555定时器是一种模拟电路和数字电路相结合的中规模集成电路,逻辑功能比较强,内部的比较器灵敏度较高。

其采用差分电路形式,构成的多谐振荡器的振荡频率受电源电压和温度的影响很小,可以方便的组成各种电路。

二、555定时器集成芯片引脚功能

1脚:外接电源负端VSS或接地,一般情况下接地。

2脚:低触发端TL,该脚电压小于1/3 VCC时有效。

3脚:输出端OUT。

4脚:直接清零端RST。当此端接低电平时,时基电路不工作,此时不论TL、TH处于何电平,时基电路输出为“0”,该端正常工作时应接高电平。

5脚:CO为控制电压端。若此脚外接电压,则可改变内部两个比较器的基准电压,当该脚不用时,需要将该脚串入一只0.01μF(103)瓷片电容接地,以防引入高频干扰。

6脚:高触发端TH,该脚电压大于2/3 VCC时有效。

7脚:放电端。该端与放电管T的集电极相连,用做定时器时电容的放电引脚。

8脚:外接电源VCC,双极型时基电路VCC的范围是4.5-16V,CMOS型时基电路VCC的范围为3-18V,一般用5V。

相关文章一例7130稳压电路引脚图

采用SOT-89及SOT-23封装,精度±2%,典型值40mV,典型值2uA,最高工作电压24V,输出电压3V。

时间:2022-07-08 05:40:31

一文看懂三端稳压管7805引脚图

在78XX、79XX系列三端稳压器中最常见的是TO-220和TO-202两种封装,这两种封装的图形以及引脚序号、引脚功能如下图:图中的引脚号标注方法,按照引脚电位从高到底的顺序标注,采用这种方式标注便于记忆。

时间:2022-07-08 05:39:26

稳压芯片7805的引脚图

7805引脚图长什么样,7805是最常用到的稳压芯片,使用比较方便,用很简单的电路即可输入一个直流稳压电源,其输出电压为5v,刚好是51系列单片机运行所需的电压。

时间:2022-05-26 15:12:01

7805三端稳压芯片的引脚图和参数及作用

7805三端稳压芯片,简称三端IC,7805顾名思义05是输出电压为5v,采用TO-220的标准封装,有过压保护、过流保护、过热保护功能,其外形与普通三极管相似,下面来看下7805稳压芯片的引脚图和参数,以及7805稳压芯片的作用。

时间:2022-05-26 15:10:20

一例555红外发射电路的原理图

一例555红外发射电路的原理图,以下是由555时基电路组成的单通道非编码式红外发射电路,如图所示,下面具体来看下。

时间:2021-11-16 11:45:19

一例555彩灯控制电路的工作原理说明

555彩灯控制电路电路图如下所示:1、工作原理彩灯控制电路以三支555为核心,组成循环触发单稳延时电路,分别控制各路的SCR循环导通,从而使彩灯依次点亮,如同流水一般。

时间:2021-11-12 16:50:04

555定时器的仿真测试说明

有关555定时器的小知识,如何对555定时器进行仿真测试,可以采用电子仿真软件MultisimV11.0来搭建仿真电路测试,以下是555定时器的完整测试过程,一起来了解下。

时间:2021-07-31 20:51:21

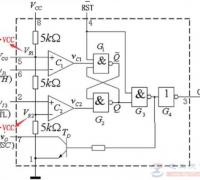

555定时器集成芯片的内部结构

有关555定时器的知识,来看一下555定时器集成芯片的内部结构是什么样的,内部包括两个电压比较器,三个5K等值串联电阻,一个 RS 触发器(由G1和G2构成),一个放电三极管T 及功率输出级。

时间:2021-07-31 20:49:45