555芯片设计的长延时定时器电路原理图

来源:电工天下时间:2021-07-31 20:36:33 作者:老电工手机版>>

555芯片长延时定时器电路

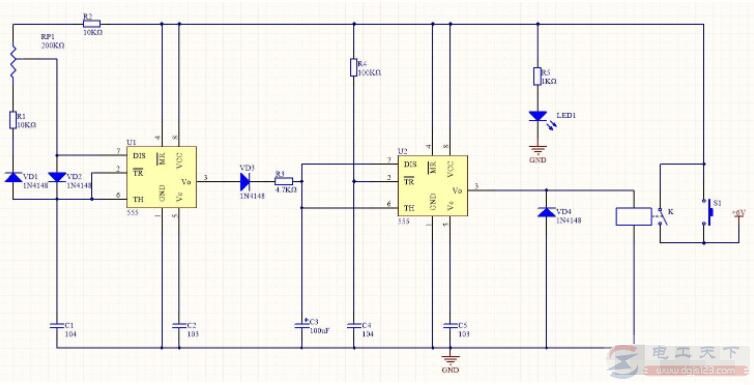

以下本电路是由2只555组成延时的定时器,电路原理图如下:

图1:长延时定时器原理图

电路原理:

由U1和R1、R2、RP1、VD1、VD2、C1组成无稳态多谐振荡器,U1的振荡方波通过VD3、R3,加至U2的第6、7脚。U2和R4、C4、R3、C3等组成一单稳延时电路。

刚开始通电时,由于C4接在 触发端第2脚与地之间,故第3脚呈现高电平,继电器K吸合,其常开触点K1-1闭合,维持给U1、U2的供电。此时,与U2的第7脚相连的集成电路内的放电管截止,因而C3开始充电。

C3的充电呈阶跃式,即U1输出方波的正脉冲,即高电平期间对其充电,由于VD3的存在,C3上的电荷不能向U1反向放电。当C3的充电电压超过+6V的2/3阈值电平时,U2复位,第3脚输出低电平,定时时间到,继电器K释放,K1-1断开,U1、U2也同时失电,电路完全停止工作。

若需要较长延时,则可以将R3更换为1MΩ的电阻,C3更换为470uF的电解电容。另外,若需要控制实际负载时,则继电器K要换成双联触点,用第二联触点控制实际负载。

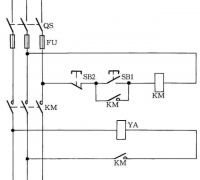

相关文章一例防止制动电磁铁延时释放线路

在交流电磁铁线圈上串入一个交流接触器常开触点,使断开电动机电源的同时断开电磁铁与电动机绕组线圈,即可使电磁铁立即释放。线路中YA为制动电磁铁,在通电后,制动解除;在断电后,YA立即制动。

时间:2022-06-03 14:05:46

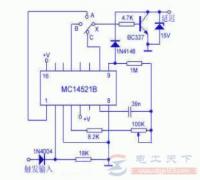

一例简单的数字式长延时电路原理图

一例简单的数字式长延时电路原理图,以下是一种数字式长延时电路,摒弃了大电解电容和高阻抗电路,延时精确度比较高,有需要的朋友参考下。

时间:2021-12-01 06:27:20

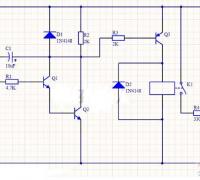

一例延时控制电路的工作过程详解

有关延时控制电路的知识,本电路由三极管组成延时控制电路,用于控制继电器的动作,当按键按下时继电器动作,延时一段时间后继电器释放,该延时控制电路的工作过程见下文。

时间:2021-11-27 11:32:55

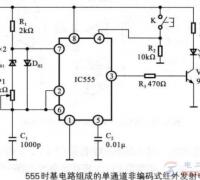

一例555红外发射电路的原理图

一例555红外发射电路的原理图,以下是由555时基电路组成的单通道非编码式红外发射电路,如图所示,下面具体来看下。

时间:2021-11-16 11:45:19

一例声控延时门灯电路的工作原理分析

声控延时门灯电路电路图如下所示:1、工作原理220V交流电经C1、R1、VD1、VD2、ZD1和C2组成的电容降压、稳压电路供给控制电路。R2、ZD2构成3V稳压电路,给音乐集成电路提供...

时间:2021-11-12 16:51:17

一例555彩灯控制电路的工作原理说明

555彩灯控制电路电路图如下所示:1、工作原理彩灯控制电路以三支555为核心,组成循环触发单稳延时电路,分别控制各路的SCR循环导通,从而使彩灯依次点亮,如同流水一般。

时间:2021-11-12 16:50:04

555定时器集成芯片引脚图及引脚功能

有关555定时器的小知识,介绍下555定时器集成芯片引脚图,以及555定时器集成芯片的八个引脚功能,比如1脚为外接电源负端VSS或接地,2脚低触发端TL,一起来了解下。

时间:2021-07-31 20:52:45

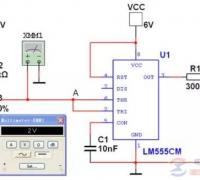

555定时器的仿真测试说明

有关555定时器的小知识,如何对555定时器进行仿真测试,可以采用电子仿真软件MultisimV11.0来搭建仿真电路测试,以下是555定时器的完整测试过程,一起来了解下。

时间:2021-07-31 20:51:21