电容谐振频率及数字电路去耦方法详解

来源:电工天下时间:2022-04-09 07:54:39 作者:老电工手机版>>

有关电容的小知识,电容中存在等效串联电感,所形成的LC串联谐振电路存在一个谐振频率,数字电路的去耦,低的ESR值比谐振频率更重要,下面具体来了解下。

电容谐振频率及数字电路去耦

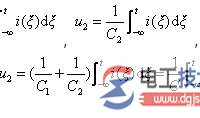

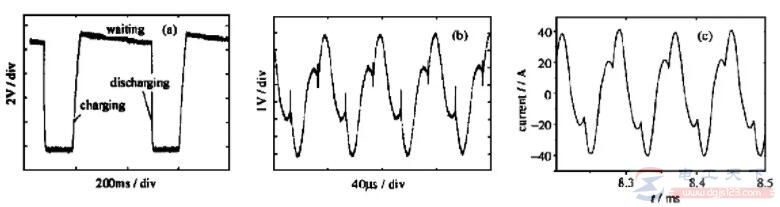

由于焊盘和引脚的原因,每个电容都存在等效串联电感(ESL),自身会形成一个串联谐振电路,LC串联谐振电路存在一个谐振频率。

随着电力的频率不同,电容的特性也随之变化,在工作频率低于谐振频率时,电容总体呈容性,在工作频率高于谐振频率时,电容总体呈感性,此时去耦电容会失去去耦的效果。

参考图:电容谐振频率

因此,如果想提高串联谐振频率,就要尽可能降低电容的等效串联电感。电容的容值选择一般取决于电容的谐振频率,不同封装的电容有不同的谐振频率。

注意数字电路的去耦,低的ESR值比谐振频率更重要,低的ESR值可以提供更低阻抗的到地通路,当超过谐振频率的电容呈现感性时,仍可以提供足够的去耦能力。

1、降低去耦电容ESL的方法

去耦电容的ESL是由于内部流动的电流引起的,使用多个去耦电容并联的方式,可以降低电容的ESL影响。将两个去耦电容以相反走向放置在一起,从而使其内部电流引起的磁通量相互抵消,可以进一步降低ESL。

说明:此方法适用于任何数目的去耦电容。

2、IC去耦电容的数目选择

在设计原理图时,经常会遇到芯片的电源引脚设计去耦电容的疸,上面介绍了去耦电容的容值选择,但是数目选择怎么确定?

理论上是每个电源引脚最好分配一个去耦电容,但在实际情况中,却经常看到去耦电容的数目少于电源引脚数目的情况,比如freescale提供的iMX233的PDK原理图中,内存SDRAM有15个电源引脚,但去耦电容的数目是10个。

3、去耦电容数目选择依据

在布局空间允许的情况下,最好做到一个电源引脚分配一个去耦电容,但在空间不足时,可以适当削减电容的数目,具体情况应根据芯片上电源引脚的具体分布决定。原因在于厂家在设计IC时,经常几个电源引脚在一起,可以共用去耦电容,减少去耦电容的数目。

相关文章电风扇电容电机的接线方法

电风扇电容电机怎么接线,单相电动机有三个抽头,先用万用表电阻挡测量三个线头间的电阻值,电阻最大的两个线头之间并联电容,另一个线头(公共端)接电源的一端。

时间:2022-08-15 20:00:58

100v10uF的电容能不能用250v10uF代替

有关电容器的选用问题,100v10uF的电容能不能用250v10uF代替,这是完全可以代替的,电容器的耐压值是标志耐压等级的,只要耐压超过100v都可以代替耐压100V的电容器,下面具体来看下。

时间:2022-06-17 11:21:45

电解电容器的检测方法及注意事项

如何进行电解电容器的检测,详细检测方法及注意事项,参考如下:电解电容的容量比一般固定电容大很多,在测量时要针对不同容量选用合适的量程。一般1~47μF间的电容,可用Rx1k挡测量,大于47μF的电容可用R×100挡测量。

时间:2022-05-30 11:07:13

不同容量固定电容器的检测方法

有关电容器好坏的检测方法,怎么检测不同容量固定电容器的好坏,分为二种情况,一种是检测10pF以下的小电容,另一种是检测0 01μF以上的固定电容,以下是具体的检测方法,供大家参考。

时间:2022-05-30 11:05:50

法拉电容正负极怎么区分,电容器正负极判断方法

有关电容器的正负极的区分方法,以法拉电容为例,介绍下如何快速区分出电容的正极与负极,不管是纽扣型法拉电容,还是牛角型或引线型的法拉电容,都可以快速区分出来。

时间:2022-05-30 11:04:56

法拉电容器技术参数及特点说明

有关法拉电容器的知识,法拉电容器是一种双电层电容器,这种电容器的技术参数包括容量、耐压值和耐温值等,与普通电容大同小异,那么法拉电容器的特点有哪些,下面具体来了解下。

时间:2022-05-30 11:03:56

用万用表检测电容器的简单方法

在电子电路中电容器有四个作用,即充放电、隔直流通交流、阻碍(容抗)和移相,在实际使用中经常需要检测电容的好坏,以下介绍了用万用表检测电容器的简单方法,供大家参考。

时间:2022-05-30 10:38:50

一文看懂电容器的充放电过程

在电容器的工作过程中,其充电与放电过程是什么样的,什么情况下表示电容器已经充满了电,什么情况下电路不会导通,下面与电工天下小编一起来了解下。

时间:2022-05-30 10:37:45

- 上一篇:电容降压的工作原理是什么?

- 下一篇:LCR电桥测电容用多大频率